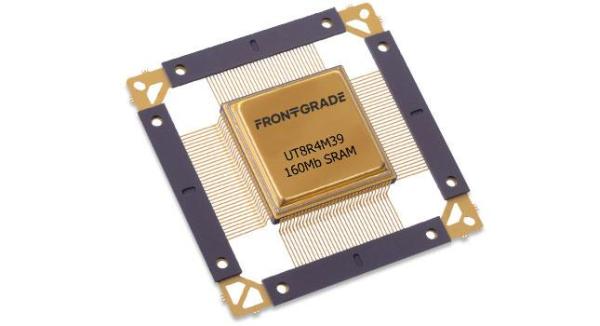

UT8R4M39 160Mb SRAM Module

| Part Number | SMD Part Number | Flight Grade | LET (MeV-cm^2/mg) | TID krad(Si) | Access Time | Configuration | Density | Supply Voltage | Package |

|---|---|---|---|---|---|---|---|---|---|

| UT8R4M39 | 5962-10207 | QML-Q, QML-Q+ | ≤110 | 100 | 25ns | 4M x 39 | 160Mb | +2.5V | 132-Lead FP |