# PRONTGRADE DATASHEET UT54ALVC2525

Clock Driver 1 to 8 Minimum Skew

2/1/2016 Version #: 1.0.0

### **Features**

- 2.0V to 3.6V Power supply operation

- Guaranteed pin-to-pin and part-to-part skew Eight LVTTL outputs with high drive strength

- Operational environment:

- > Total-dose tolerance: 100 to 300 krad(Si), or 1 Mrad(Si)

- > SEL Immune to a LET of 111 MeV-cm2/mg HiRel temperature range: -55°C to +125°C

- · Packaging options:

- 14-Lead Ceramic Flatpack

- Standard Microcircuit Drawing: 5962-06233

- > QML Q and V

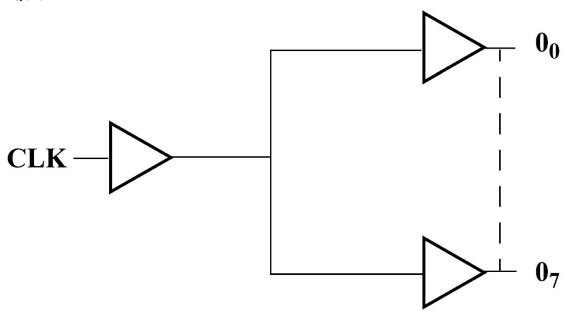

Figure 1: UT54ALVC2525 Block Diagram

### **Introduction**

The UT54ALVC2525 is a low-voltage, minimum skew, one-to-eight clock driver. The UT54ALVC2525 distributes a single clock to eight, high-drive, outputs with low skew across all outputs during both the  $t_{PLH}$  and  $t_{PHL}$  transitions making it ideal for signal generation and clock distribution. The output pins act as a single entity and will follow the state of the CLK pin.

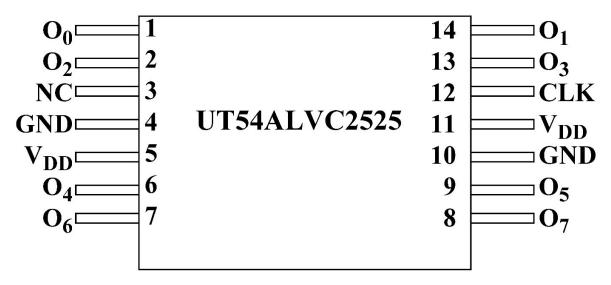

Figure 2. 14-Lead Ceramic Flatpack Pinouts

# **Pin Description**

| Flatpack Pin No.         | Name            | 1/0 | Туре  | Description                                                                                |

|--------------------------|-----------------|-----|-------|--------------------------------------------------------------------------------------------|

| 12                       | CLK             | I   | LVTTL | Primary reference clock input. This pin must be driven by an LVTTL or LVCMOS clock source. |

| 3                        | N/C             |     |       | No connect.                                                                                |

| 1, 2, 6, 7, 8, 9, 13, 14 | On              | О   | LVTTL | Eight output clocks.                                                                       |

| 5, 11                    | V <sub>DD</sub> | PWR | Power | Power supply for internal circuitry and output buffers.                                    |

| 4, 10                    | VSS             | PWR | Power | Ground                                                                                     |

# **Operational Environment**

The UT54ALVC2525 incorporates special design, layout, and process features which allows operation in a limited HiRel environment

| Parameter                                                 | Lin    | nit Units               |

|-----------------------------------------------------------|--------|-------------------------|

| Total Ionizing Dose (TID)                                 | >1E6   | rads(Si)                |

| Single Event Latchup (SEL) <sup>1, 2</sup>                | >111   | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Upset (SEU) LET (@2.0V) <sup>3,5</sup> | 52     | MeV-cm <sup>2</sup> /mg |

| Onset Single Event Upset (SEU) LET (@3.0V) 4,5            | 66     | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence                                           | 1.0E14 | n/cm <sup>2</sup>       |

| Dose Rate Upset                                           | TBD    | rads(Si)/sec            |

| Dose Rate Survivability                                   | TBD    | rads(Si)/sec            |

#### Notes:

- 1. The UT54ALVC2525 is latchup immune to particle LETs >111 MeV-cm2/mg.

- 2. SEL temperature and voltage conditions of TC = +125°C,  $V_{DD}$  = 3.6V.

- 3. SEU temperature and voltage conditions of TC =  $+25^{\circ}$ C,  $V_{DD}$  = 2.0V. Tested at 200MHz.

- 4. SEU temperature and voltage conditions of TC = +25°C, V<sub>DD</sub> = 3.0V. Tested at 200MHz.

- 5. For the UT54ALVC2525 SET performance at select operating frequency data ranges, please contact the factory.

## **Absolute Maximum Ratings:**<sup>1</sup>

(Referenced to V<sub>SS</sub>)

| Symbol             | Description                                  | Limits                        | Units |

|--------------------|----------------------------------------------|-------------------------------|-------|

| V <sub>DD</sub>    | Core Power Supply Voltage                    | -0.3 to 4.0                   | V     |

| V <sub>IN</sub>    | Voltage Any Clock Input                      | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| V <sub>OUT</sub>   | Voltage Any Clock Output                     | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| I <sub>1</sub>     | DC Input Current                             | ±10                           | mA    |

| P <sub>D</sub>     | Maximum Power Dissipation                    | 1                             | W     |

| T <sub>STG</sub>   | Storage Temperature                          | -65 to +150                   | °C    |

| Tı                 | Maximum Junction Temperature 2               | +150                          | °C    |

| <del>O</del> JC    | Thermal Resistance, Junction to Case         | 20                            | °C/W  |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) - Class II | >3000                         | V     |

### Notes:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and

functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this

specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

and performance.

- 2. Maximum junction temperature may be increased to +175°C during burn-in and steady-static life.

## **Recommended Operating Conditions:**

| Symbol           | Description                | Limits               | Units |

|------------------|----------------------------|----------------------|-------|

| $V_{DD}$         | Core Operating Voltage     | 2.0 to 3.6           | V     |

| V <sub>IN</sub>  | Voltage Clock Input        | 0 to V <sub>DD</sub> | V     |

| V <sub>OUT</sub> | Voltage Any Clock Output   | 0 to V <sub>DD</sub> | V     |

| T <sub>C</sub>   | Case Operating Temperature | -55 to +125          | °C    |

# Electrical Characteristics (Pre- and Post-Radiation)\* $(V_{DD} = 2.0V \text{ to } 3.6V; TC = -55^{\circ}C \text{ to } +125^{\circ}C)$

| Symbol                          | Description                  | Conditions                                                                                               | $V_{DD}$                      | MIN                     | MAX                    | Units      |

|---------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|------------------------|------------|

| V <sub>IH</sub> <sup>1</sup>    | High level input voltage     |                                                                                                          | 2.0V<br>2.75V<br>3.0V<br>3.6V | 1.25 1.5<br>1.75<br>2.0 |                        | V          |

| $V_{lL}^1$                      | Low level input voltage      |                                                                                                          | 2.0V<br>2.75V<br>3.0V<br>3.6V |                         | 0.7 0.8<br>0.8<br>0.8  | V          |

| V <sub>OL</sub>                 | Low level output voltage     | I <sub>OL</sub> = 12mA<br>I <sub>OL</sub> = 12mA<br>I <sub>OL</sub> = 12mA<br>I <sub>OL</sub> = 12mA     | 2.0V<br>2.75V<br>3.0V<br>3.6V |                         | 0.45<br>0.4 0.4<br>0.4 | V          |

| V <sub>OH</sub>                 | High level output voltage    | I <sub>OH</sub> = -12mA<br>I <sub>OH</sub> = -12mA<br>I <sub>OH</sub> = -12mA<br>I <sub>OH</sub> = -12mA | 2.0V<br>2.75V<br>3.0V<br>3.6V | 1.5 2.2<br>2.4<br>3.0   |                        | V          |

| l <sub>os</sub> <sup>2</sup>    | Short-circuit output current | V <sub>OUT</sub> = V <sub>DD</sub> and V <sub>SS</sub>                                                   | 2.0V<br>3.6V                  | -200<br>-300            | 200<br>300             | mA         |

| I <sub>IL</sub>                 | Input leakage current        | $V_{IN} = V_{DD}$ or $V_{SS}$                                                                            | 3.6V                          | -1                      | 1                      | μΑ         |

| I <sub>DDQ</sub>                | Quiescent Supply Current     | $V_{IN} = V_{DD}$ or $V_{SS}$                                                                            | 2.0V<br>3.6V                  |                         | 1.0 1.0                | mA         |

| P <sub>TOTAL</sub> <sup>3</sup> | Total power dissipation      | CL = 20pF                                                                                                | 2.0V<br>2.75V<br>3.0V<br>3.6V |                         | 1.2 2.7<br>3.5<br>5.2  | mW/<br>MHz |

| C <sub>IN</sub> <sup>4</sup>    | Input capacitance            | f = 1MHz                                                                                                 | 0V                            |                         | 15                     | pF         |

| C <sub>OUT</sub> <sup>4</sup>   | Output capacitance           | f = 1MHz                                                                                                 | 0V                            |                         | 15                     | pF         |

- 2. Supplied as a design limit. Neither guaranteed nor tested.

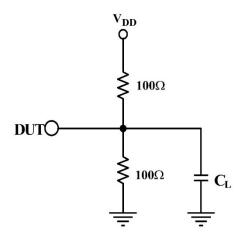

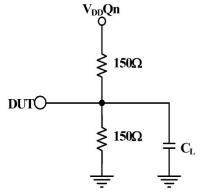

- 3. When measuring the dynamic supply current, all outputs are loaded in accordance with the equivalent test load defined in figure 3.

- 4. Capacitance is measured for initial qualification and when design changes may affect the input/output capacitance. Capacitance is measured between the designated terminal and the VSS at a frequency of 1MHz and a signal amplitude of 50mV rms maximum.

<sup>\*</sup> Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to a TID level of 1.0E6 rad(Si).

<sup>1.</sup> Functional tests are conducted in accordance with MIL-STD-883 with the following test conditions: VIH=VIH(min) +20%, -0% VIL=VIL(max)+0%, -50%, as specified herein for the LVTTL and LVCMOS inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to VIH(min), VIL (max).

# AC Electrical Characteristics (Pre- and Post-Radiation)\* $(V_{DD} = 2.0V \text{ to } 3.6V; TC = -55^{\circ}C \text{ to } +125^{\circ}C)$

| Symbol                                       | Description                                                                                                 | Condition                                                                                                                                   | $V_{DD}$                      | MIN                        | MAX                        | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|----------------------------|------|

| t <sub>R</sub> , t <sub>F</sub> <sup>3</sup> | Input rise/fall time                                                                                        | V <sub>IH</sub> (min) - V <sub>IL</sub> (max)                                                                                               | 3.6V                          |                            | 20                         | ns/V |

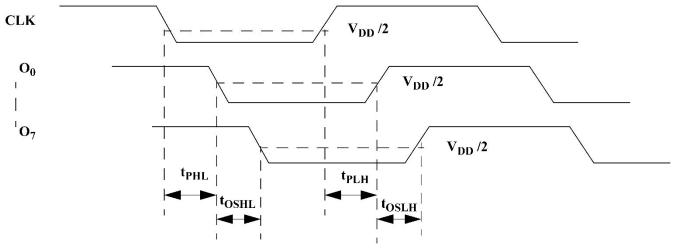

| t <sub>PHL</sub> 1,2                         | Propagation delay: CLK to On, high-to-low transition                                                        | Measured as transition time between $V_{IN} = V_{DD} \div 2$ to $V_{OUT} = V_{DD} \div 2$                                                   | 2.0V<br>2.75V<br>3.0V<br>3.6V | 3.5<br>3.0<br>2.75<br>2.25 | 7.5<br>5.5<br>5.25<br>4.75 | ns   |

| t <sub>PLH</sub> 1,2                         | Propagation delay: CLK to On, low-to-high transition                                                        | Measured as transition time between $VIN = V_{DD} \div 2$ to $V_{OUT} = V_{DD} \div 2$                                                      | 2.0V<br>2.75V<br>3.0V<br>3.6V | 3.25<br>2.75<br>2.5<br>2.0 | 7.25<br>5.25<br>5.0<br>4.5 | ns   |

| t <sub>OSHL</sub> <sup>2,4,5</sup>           | Maximum skew: common edge, output-to-output, high-to-low transition                                         | Measured as $V_{On} = V_{DD} \div 2$ to $V_{Om} = V_{DD} \div 2$<br>where $n,m = 0$ to 7; $n$ not equal to $m$ @ $f_{CLK} = 200 MHz$        | 2.0V<br>3.6V                  |                            | 0.15 0.25                  | ns   |

| tOSLH 2, 4, 5                                | Maximum skew: common edge, output-to-output, low-to-high transition                                         | Measured as $V_{On}=V_{DD} \div 2$ to $V_{Om}=V_{DD} \div 2$ where $n,m=0$ to 7; $n$ not equal to $m$ @ fCLK = 200MHz                       | 2.0V<br>3.6V                  |                            | 0.15 0.25                  | ns   |

| tORISE & 3<br>tOFALL                         | Output rise/fall time                                                                                       | Measured as transition time between 20% * V <sub>OL</sub> and 80% * V <sub>OH</sub> @ fCLK = 100MHz                                         | 2.0V<br>3.6V                  |                            | 2.4 2.0                    | ns   |

| tPART 4, 5                                   | Part-part skew                                                                                              | Skew between the same output of any two devices under identical settings and conditions (V <sub>DD</sub> , temp, air flow, frequency, etc). | 2.0V<br>3.6V                  |                            | 0.1<br>0.15                | ns   |

| tPBAL 1, 4                                   | Propagation delay balance:<br>difference between same<br>output, low-to-high and<br>high-to-low transitions | Measured as transition time between $V_{IN} = V_{DD} \div 2$ to VOUT = $V_{DD} \div 2$                                                      | 2.0V<br>2.75V<br>3.0V<br>3.6V |                            | 0.43 0.3<br>0.26<br>0.21   | ns   |

### Notes:

\*Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to a TID level of 1.0E6 rad(Si).

- 1. Test load = 40pF, terminated to V<sub>DD</sub>÷2. All outputs are equally loaded. Reference Figure 3 for clock output loading.

- 2. Reference Figure 4 for AC timing diagram.

- 3. Supplied only as a design guideline, neither tested nor guaranteed.

- 4. Guaranteed by characterization, but not tested.

- 5. Test load = 40pF, terminated to V<sub>DD</sub>÷2. All outputs are equally loaded. Reference Figure 5 for clock output loading.

Figure 3. Test Load Circuit for Dynamic Power Supply Current and AC Measurements

#### Note:

1. This is not the recommended termination for normal user operation.

Figure 4. AC Timing Diagram

Figure 5. Test Load Circuit for tOSHL and tOSLH Measurements

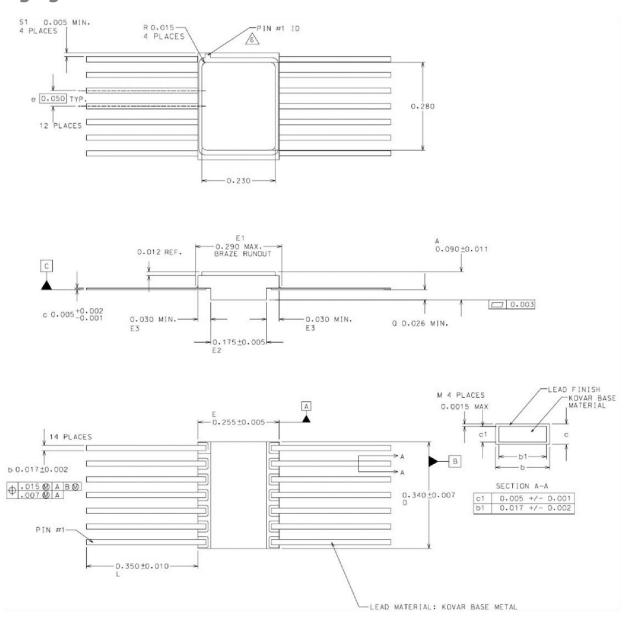

# **Packaging**

Figure 6. 14-Pin Flatpack Package

- 1. All exposed metallized areas are gold plated over electroplated nickel per MIL-PRF-38535.

- 2. The lid is electrically connected to VSS.

- 3. Lead finishes are in accordance with MIL-PRF-38535.

- 4. Dimension symbol is in accordance with MIL-PRF-38533.

- 5. Lead position and colanarity are not measured.

- 6. ID mark symbol is vendor option.

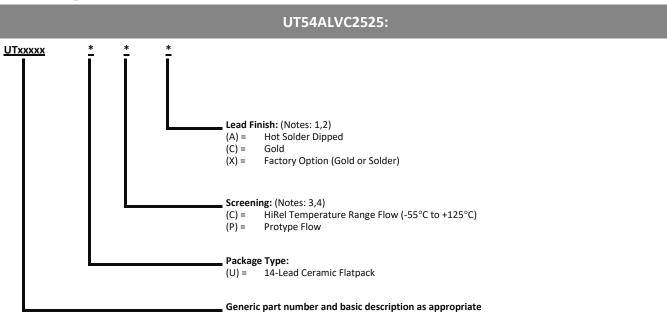

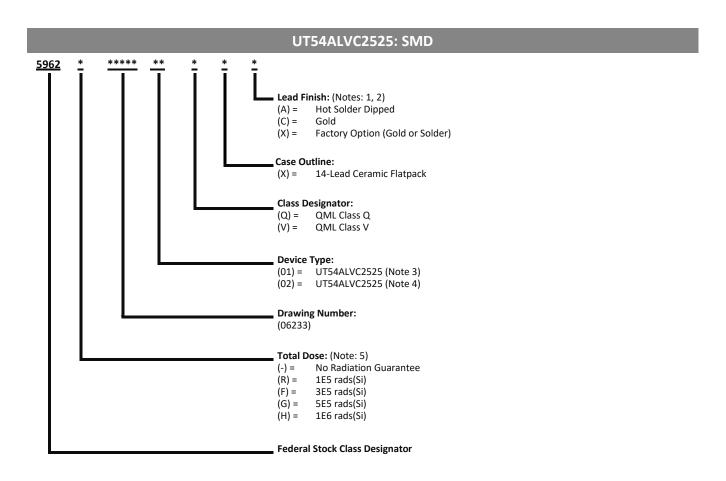

# **Ordering Information**

- 1. Lead finish (A, C, or X) must be specified.

- 2. If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3. Prototype flow per CAES Manufacturing Flows Document. Tested at 25°C only. Lead finish is GOLD ONLY. Radiation neither tested nor guaranteed.

- 4. HiRel Temperature Range flow per CAES Manufacturing Flows Document. Devices are tested at -55°C, room temp, and 125°C. Radiation neither tested nor guaranteed.

- 1. Lead finish (A, C, or X) must be specified.

- 2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold)

- 3. Available to a maximum RHA level of H.

- 4. Available to a maximum RHA level of R. Device is irradiated at a dose rate = 50-300 rads(Si)/s in accordance with MIL-STD-883, Method 1019, Condition A, and is guaranteed to a maximum total dose specified. The effective dose rate after extended room temperature anneal = 1 rads(Si)/s per MIL-STD-883, Method 1019, Condition A, section 3.11.2. The total dose specification for these devices only applies to a low dose rate environment.

- 5. Total dose radiation must be specified when ordering. QML Q and QML V are not available without radiation hardening.

# **Revision History**

| Date | Revision # | Author | Change Description       | Page # |

|------|------------|--------|--------------------------|--------|

| 2-16 | 1.0.0      | ВМ     | Added datasheet template |        |

|      |            |        |                          |        |

|      |            |        |                          |        |

|      |            |        |                          |        |

### **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                   |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Frontgrade Colorado Springs LLC (Frontgrade) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.