# FRONTGRADE

**APPLICATION NOTE**

UT32M0R500

Comparators

5/31/2022 Version #: 1.0.0

**Table 1: Cross Reference of Applicable Products**

| Product Name Manufacturer Part<br>Number |            | SMD#       | Device Type |

|------------------------------------------|------------|------------|-------------|

| Arm Cortex M0+                           | UT32M0R500 | 5962-17212 | 01, 02      |

#### 1.0 Introduction

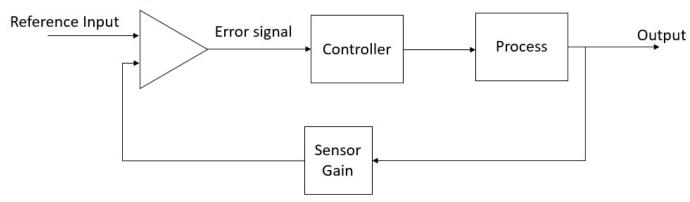

The UT32M0R500 analog Comparator compares two analog voltages and outputs a digital output. The comparator has two inputs: positive (+) and negative (-). The positive input (CMP0A) gets the external signal to be measured against different references on the negative input, which are either DAC0, DAC1, CMP0B or VREF. If CMP0A is greater than the negative (-) input, the comparator output will be logic one, logic zero otherwise. The comparator output is directly read by software. In a feedback loop approach, the comparator is used to compare the feedback signal against a reference input and output an error signal, see example block diagram below.

## Comparator

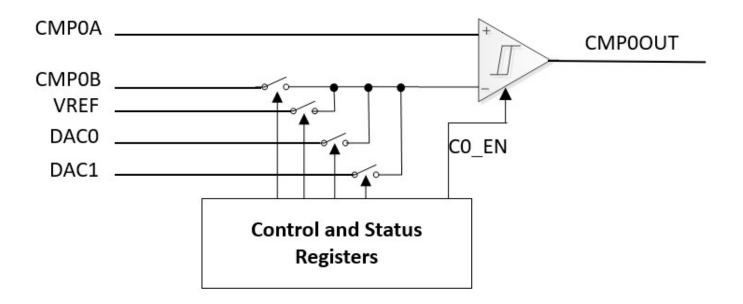

# 2.0 UT32M0R500 Comparator

The figure below shows the UT32M0R500 Comparator peripheral. The comparator has the following key features:

- Two High-speed Analog Comparators

- Hysteresis on Inputs

- · Rail-to-Rail Input Common-Mode Range

- · Four selectable inputs to the negative input of each comparator

- Low Power Shutdown Mode

#### 2.1 UT32M0R500 Comparator Hardware

There are two Comparators within the UT32M0R500 Comparator module. The Comparator module is mapped to the memory region from 0x4000\_E000 to 0x4000\_EFFF. It has 2 registers. For more information on each register, refer to Chapter 16 of the UT32M0R500 Functional Manual.

#### 2.2 Comparator Control Register

The Control Register (CTRL) enables and selects the reference input. The reference input is selected to be either COMPOB, VREF, DACO or DAC1, bits [2:1], for Comparator 0. Comparator enable (CO\_EN), bit [0], enables the Comparator 0 unit. Comparator 1 uses the same Control register with similar configurations, see register below.

#### **Description of the Control Register**

| BIT Number(s) | BIT Name   | RESET State | Description                                                                                                                                    |  |

|---------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31-7          | Reserved   | [000]       |                                                                                                                                                |  |

| 6-5           | C1_NEG_SEL | 00          | Comparator #1 negative input selector: 11: Input from DAC1 10: Input from DAC0 01: Input from pin CMP1B 00: Input from voltage reference ~VREF |  |

| 4             | C1_EN      | 0           | Comparator #1 enable selector 1: Comparator #1 enabled 0: Power down Comparator #1; CMP1OUT will be driven to '0'                              |  |

| 3             | RESERVED   | 0           |                                                                                                                                                |  |

| 2-1           | CO_NEG_SEL | 00          | Comparator #0 negative input selector: 11: Input from DAC1 10: Input from DAC0 01: Input from pin CMP0B 00: Input from voltage reference ~VREF |  |

| 0             | CO_EN      | 0           | Comparator #0 enable selector  1: Comparator #0 enabled  0: Power down Comparator #0; CMP0OUT will be driven to '0'                            |  |

#### 2.3 Comparator Initialization

The code below initializes Comparator 0.

```

// init the COMPs

89

90

DUAL CMPR StructInit (&DUAL CMPR InitStruct);

91

92

DUAL CMPR InitStruct.DUAL CMPR 0.CX NEG SEL = VREF;

DUAL CMPR InitStruct.DUAL CMPR 1.CX NEG SEL = VREF;

93

94

DUAL CMPR Init (DUAL CMPR, &DUAL CMPR InitStruct);

95

96

97

DUAL CMPR Cmd (DUAL CMPR, DUAL CMPRO, CMPR ENABLE);

DUAL CMPR Cmd (DUAL CMPR, DUAL CMPR1, CMPR ENABLE);

98

```

#### 2.4 Reading Comparator 0

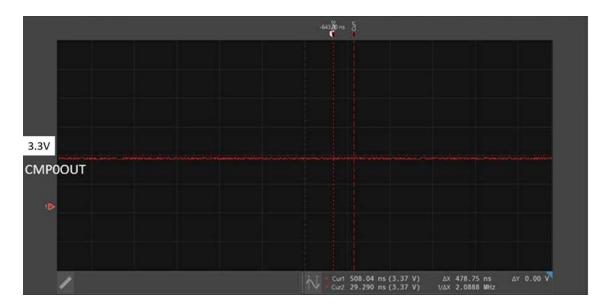

The code below reads Comparator 0 value and outputs it to the terminal; the figure below shows CMP0OUT going high when the positive input is higher than VREF (1.2 V).

### 3.0 Conclusion

Many applications use a feedback loop approach and the comparator is used to compare the feedback signal against a reference input and outputs an error signal. With two High-speed Analog Comparators, hysteresis on Inputs and Rail-to-Rail Input Common-Mode Range, the UT32M0R500 comparators are key to controlling the system in the feedback loop.

# **Revision History**

| Date       | Revision # | Author | Change Description | Page # |

|------------|------------|--------|--------------------|--------|

| 05/31/2022 | 1.0.0      | JA     | Initial Release    |        |

|            |            |        |                    |        |

|            |            |        |                    |        |

|            |            |        |                    |        |

## **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> .  Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                             |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                    |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents, rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.