# UT54ACS164245SEI

### Features

- Flexible voltage operation

- 5V bus to 3.3V bus; 5V bus to 5V bus

- 3.3V bus to 5V bus; 3.3V bus to 3.3V bus

- Cold sparing

- $1M\Omega$  minimum input impedance power-off

- Warm sparing

- Guaranteed output tri-state while one power supply is "off" and the other is "on"

- $1 \mbox{M} \Omega$  minimum input impedance power-off

- 0.6µm CRH CMOS Technology

- Operational Environment:

- Total dose: 100 krads(Si)

- Single Event Latchup immune

- High speed, low power consumption

- · Schmitt trigger inputs to filter noisy signals

- Available QML Q or V processes

- Standard Microcircuit Drawing 5962-98580

- Device Types 06 and 07

- Package:

- 48-lead flatpack, 25 mil pitch (.390 x .640), wgt 1.4 Grams

### Description

The 16-bit wide UT54ACS164245SEI MultiPurpose transceiver is built using CAES CRH technology. This high speed, low power UT54ACS164245SEI transceiver is designed to perform multiple functions including: asynchronous twoway communication, schmitt input buffering, voltage translation, cold and warm sparing. With either or both  $V_{DD1}$  and  $V_{DD2}$  are equal to zero volts, the UT54ACS164245SEI outputs and inputs present a minimum impedance of  $1M\Omega$  making it ideal for "cold spare" applications. Balanced outputs and low "on" output impedance make the UT54ACS164245SEI well suited for driving high capacitance loads and low impedance backplanes. The UT54ACS164245SEI enables system designers to interface 3.3 volt CMOS compatible components with 5 volt CMOS components. For voltage translation, the A port interfaces with the 3.3 volt bus; the B port interfaces with the 5 volt bus. The direction control (DIRx) controls the direction of data flow. The output enable ( $\overline{OEx}$ ) overrides the direction control and disables both ports. These signals can be driven from either port A or B. The direction and output enable controls operate these devices as either two independent 8-bit transceivers or one 16-bit transceiver.

# UT54ACS164245SEI

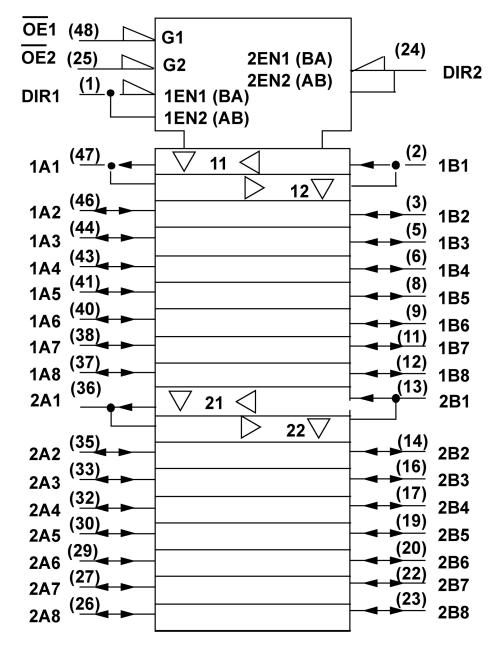

## Logic Symbol

## **Pin Description**

| Pin Names | Description                                  |

|-----------|----------------------------------------------|

| OEx       | Output Enable Input (Active Low)             |

| DIRx      | Direction Control Inputs                     |

| хАх       | Side A Inputs or 3-State Outputs (3.3V Port) |

| хВх       | Side B Inputs or 3-State Outputs (5V Port)   |

# UT54ACS164245SEI

### **Function Table**

| Enable<br>OEx | Direction<br>DIRx | Operation       |

|---------------|-------------------|-----------------|

| L             | L                 | B Data To A Bus |

| L             | Н                 | A Data To B Bus |

| Н             | Х                 | Isolation       |

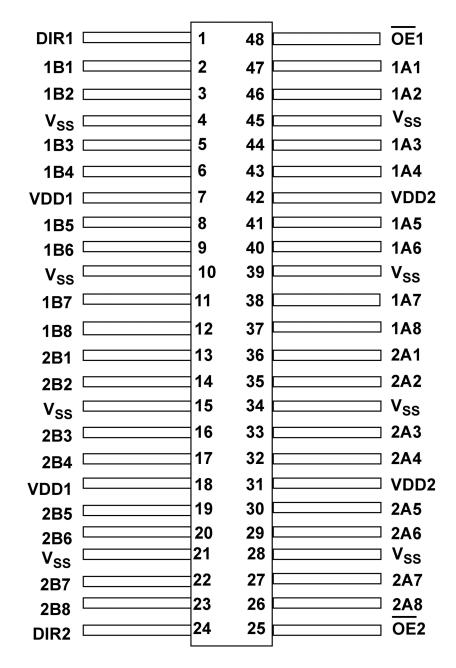

### Pinouts

48-Lead Flatpack Top View

# UT54ACS164245SEI

### **IO Guidelines**

All inputs are 5 volt tolerant. When VDD2 is at 3.3 volts, either 3.3 or 5 volt CMOS logic levels can be applied to all control inputs. It is recommended that all unused inputs be tied to VSS through a  $1K\Omega$  to  $10K\Omega$  resistor.

It's good design practice to tie the unused input to VSS via a resistor to reduce noise susceptibility. The resistor protects the input pin by limiting the current from high going variations in VSS.

The number of inputs that can be tied to the resistor pull-down can vary. It is up to the system designer to choose how many inputs are tied together by figuring out the max load the part can drive while still meeting system performance specs. Input signal transitions should be driven to the device with a rise and fall time that is <100ms.

| Port B          | Port A          | Operation          |

|-----------------|-----------------|--------------------|

| 5 Volts         | 3.3 Volts       | Voltage Translator |

| 5 Volts         | 5 Volts         | Non Translating    |

| 3.3 Volts       | 3.3 Volts       | Non Translating    |

| V <sub>SS</sub> | V <sub>SS</sub> | Cold Spare         |

| V <sub>SS</sub> | 3.3V or 5V      | Port A Warm Spare  |

| 3.3V or 5V      | V <sub>SS</sub> | Port B Warm Spare  |

### **Power Table**

## **Power Application Guidelines**

For proper operation, connect power to all V<sub>DD</sub> pins and ground all V<sub>SS</sub> pins (i.e., no floating V<sub>DD</sub> or V<sub>SS</sub> input pins). By virtue of the UT54ACS164245SEI warm spare feature, power supplies V<sub>DD1</sub> and V<sub>DD2</sub> may be applied to the device in any order. To ensure the device is in cold spare mode, both supplies, V<sub>DD1</sub> and V<sub>DD2</sub> must be equal to V<sub>SS</sub> +/- 0.3V. Warm spare operation is in effect when one power supply is >1V and the other power supply is equal to V<sub>SS</sub> +/- 0.3V. If V<sub>DD1</sub> has a power on ramp longer than 1 second, then V<sub>DD2</sub> should be powered on first to ensure proper control of DIRx and  $\overline{OEx}$ . During normal operation of the part, after power-up, ensure VDD1≥VDD2.

### Warm Spare

By definition, warm sparing occurs when half of the chip receives its normal  $V_{DD}$  supply value while the  $V_{DD}$  supplying the other half of the chip is set to 0.0V. When the chip is "warm spared", the side that has  $V_{DD}$  set to a normal operational value is "actively" tri-stated because the chip's internal OE signal is forced low. The side of the chip that has  $V_{DD}$  set to 0.0V is "passively" tri-stated by the cold spare circuitry. In order to minimize transients and current consumption, the user is encouraged to first apply a high level to the  $\overline{OEx}$  pins and then power down the appropriate supply.

### **Cold Spare**

The UT54ACS164245SEI places the device into "Cold Spare" mode when BOTH supplies are set to  $V_{SS}$  +/\_0.25V with a maximum 1K $\Omega$  impedance between  $V_{DDx}$  and  $V_{SS}$ . While in Cold Spare, the device places all outputs into a high impedance state (see DC electrical parameters, Ics).

# UT54ACS164245SEI

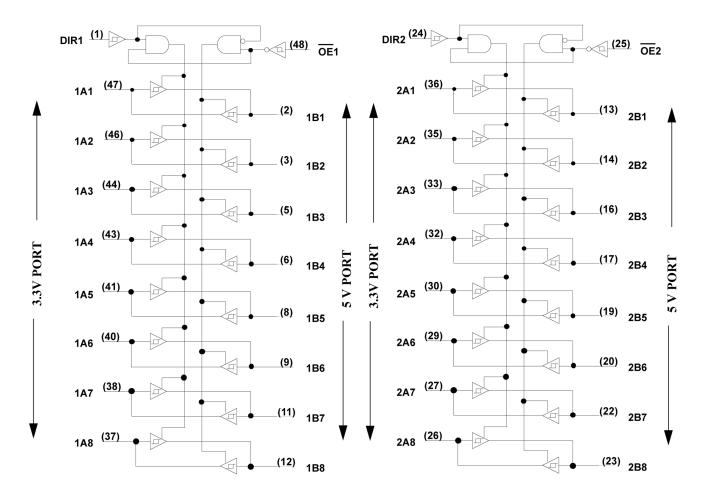

### Logic Diagram

## **Operational Environment**<sup>1</sup>

| Parameter                    | Limit  | Units                   |

|------------------------------|--------|-------------------------|

| Total Dose                   | 1.0E5  | rad(Si)                 |

| SEL Immune                   | >114   | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence <sup>2</sup> | 1.0E14 | n/cm <sup>2</sup>       |

#### Notes:

1) Logic will not latchup during radiation exposure within the limits defined in the table.

2) Not tested, inherent to CMOS technology.

# UT54ACS164245SEI

### Absolute Maximum Ratings <sup>1</sup>

| Symbol                              | Parameter                           | Limit (Mil Only)          | Units |

|-------------------------------------|-------------------------------------|---------------------------|-------|

| $V_{\rm I/O}$ (Port B) <sup>2</sup> | Voltage any pin during operation    | 3 to V <sub>DD1</sub> +.3 |       |

| $V_{\rm I/O}$ (Port A) <sup>2</sup> | Voltage any pin during operation    | 3 to V <sub>DD2</sub> +.3 |       |

| V <sub>DD1</sub>                    | Supply voltage                      | -0.3 to 6.0               | V     |

| V <sub>DD2</sub>                    | Supply voltage                      | -0.3 to 6.0               | V     |

| T <sub>STG</sub>                    | Storage Temperature range           | -65 to +150               | °C    |

| Tı                                  | Maximum junction temperature        | +175                      | °C    |

| Θις                                 | Thermal resistance junction to case | 20                        | °C/W  |

| II                                  | DC input current                    | ±10                       | mA    |

| P <sub>D</sub>                      | Maximum power dissipation           | 1                         | W     |

Notes:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2) For Cold Spare mode ( $V_{DD} = V_{SS}$ ),  $V_{I/O}$  may be -0.3V to the maximum recommended operating  $V_{DD} + 0.3V$ .

### **Dual Supply Operating Conditions**

| Symbol                   | Parameter             | Limit U                  |    |

|--------------------------|-----------------------|--------------------------|----|

| V <sub>DD1</sub>         | Supply voltage        | 3.0 to 3.6 or 4.5 to 5.5 | V  |

| V <sub>DD2</sub>         | Supply voltage        | 3.0 to 3.6 or 4.5 to 5.5 |    |

| V <sub>IN</sub> (Port B) | Input voltage any pin | 0 to V <sub>DD1</sub>    |    |

| V <sub>IN</sub> (Port A) | Input voltage any pin | 0 to V <sub>DD2</sub>    |    |

| T <sub>C</sub>           | Temperature range     | -55 to + 125             | °C |

# UT54ACS164245SEI

## DC Electrical Characteristics <sup>1</sup>

$(T_c = -55^{\circ}C \text{ to } +125^{\circ}C \text{ for } "C" \text{ screening and } -40^{\circ}C \text{ to } +125^{\circ}C \text{ for } "W" \text{ screening})$

| Symbol            | Parameter                                                    | Condition                                                                                        | MIN                                            | MAX               | Unit |

|-------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|------|

| $V_{T}^{+}$       | Schmitt Trigger, positive going threshold <sup>2</sup>       | $V_{DD}$ from 3.0 to 5.5                                                                         |                                                | .7V <sub>DD</sub> | V    |

| V <sub>T</sub> -  | Schmitt Trigger, negative going threshold <sup>2</sup>       | $V_{DD}$ from 3.0 to 5.5                                                                         | .3V <sub>DD</sub>                              |                   | V    |

| $V_{\text{H1}}$   | Schmitt Trigger range of hysteresis                          | $V_{DD}$ from 4.5 to 5.5                                                                         | 0.6                                            |                   | V    |

| $V_{\text{H2}}$   | Schmitt Trigger range of hysteresis                          | V <sub>DD</sub> from 3.0 to 3.6                                                                  | 0.4                                            |                   | V    |

| $\mathbf{I}_{IN}$ | Input leakage current                                        |                                                                                                  | -1                                             | 3                 | μA   |

| I <sub>OZ</sub>   | Three-state output leakage current                           | $V_{DD}$ from 3.6 to 5.5<br>$V_{IN} = V_{DD}$ or $V_{SS}$                                        | -1                                             | 3                 | μA   |

| I <sub>CS</sub>   | Cold sparing input leakage current <sup>3</sup>              | $\begin{array}{l} V_{IN}=5.5\\ V_{DD}=V_{SS} \end{array}$                                        | -1                                             | 5                 | μA   |

| I <sub>ws</sub>   | Warm sparing input leakage current<br>(any pin) <sup>3</sup> |                                                                                                  | -1                                             | 5                 | μΑ   |

| I <sub>OS1</sub>  | Short-circuit output current <sup>6, 10</sup>                | $V_{O} = V_{DD}$ or $V_{SS}$<br>$V_{DD}$ from 4.5 to 5.5                                         | -200                                           | 200               | mA   |

| I <sub>OS2</sub>  | Short-circuit output current 6, 10                           | $V_{\text{O}} = V_{\text{DD}} \text{ or } V_{\text{SS}}$ $V_{\text{DD}} \text{ from 3.0 to 3.6}$ | -100                                           | 100               | mA   |

| V <sub>OL1</sub>  | Low-level output voltage <sup>4</sup>                        | $I_{OL}=8mA$ $I_{OL}=100\mu A$ $V_{DD}=4.5$                                                      |                                                | 0.4<br>0.2        | v    |

| V <sub>OL2</sub>  | Low-level output voltage <sup>4</sup>                        | $    I_{OL} = 8mA     I_{OL} = 100 \mu A     V_{DD} = 3.0 $                                      |                                                | 0.5<br>0.2        | v    |

| V <sub>OH1</sub>  | High-level output voltage <sup>4</sup>                       | $I_{OH}=-8mA$<br>$I_{OH}=-100\mu A$<br>$V_{DD}=4.5$                                              | V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 0.2 |                   | v    |

| V <sub>OH2</sub>  | High-level output voltage <sup>4</sup>                       |                                                                                                  | V <sub>DD</sub> - 0.9<br>V <sub>DD</sub> - 0.2 |                   | v    |

# UT54ACS164245SEI

| Symbol              | Parameter                                     | Condition                                              | MIN | MAX        | Unit       |

|---------------------|-----------------------------------------------|--------------------------------------------------------|-----|------------|------------|

| P <sub>total1</sub> | Power dissipation 5, 7, 8                     | $C_L = 50 pF$<br>$V_{DD}$ from 4.5 to 5.5              |     | 2.0        | mW/<br>MHz |

| P <sub>total2</sub> | Power dissipation 5, 7, 8                     | $C_{L} = 50 pF$<br>V <sub>DD</sub> from 3.00 to 3.6    |     | 1.5        | mW/<br>MHz |

|                     | Standby Supply Current $V_{DD1}$ or $V_{DD2}$ | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{DD} = 5.5$ |     |            |            |

| $\mathbf{I}_{DDQ}$  | Pre-Rad 25°C                                  | $\overline{OE} = V_{DD}$                               |     | 60         | μA         |

|                     | Pre-Rad -55°C to +125°C<br>Post-Rad 25°C      | $\overline{OE} = V_{DD}$ $\overline{OE} = V_{DD}$      |     | 100<br>100 | μΑ<br>μΑ   |

| CIN                 | Input capacitance <sup>9</sup>                | f = 1MHz @ 0V<br>V <sub>DD</sub> from 3.0 to 5.5       |     | 15         | pF         |

| Соит                | Output capacitance <sup>9</sup>               | f = 1MHz @ 0V<br>V <sub>DD</sub> from 3.0 to 5.5       |     | 15         | pF         |

- 1) All specifications valid for radiation dose  $\leq$  1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions:  $V_{IH} = V_{IH}(min) + 20\%$ , 0%;  $V_{IL} = V_{IL}(max) + 0\%$ , 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to  $V_{IH}(min)$  and  $V_{IL}(max)$ .

- 3) This parameter is unaffected by the state of  $\overline{OE}x$  or DIRx.

- Per MIL-PRF-38535, for current density ≤ 5.0E5 amps/cm<sup>2</sup>, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765 pF-MHz.

- 5) Guaranteed by characterization.

- 6) Not more than one output may be shorted at a time for maximum duration of one second.

- 7) Power does not include power contribution of any CMOS output sink current.

- 8) Power dissipation specified per switching output.

- 9) Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and V<sub>ss</sub> at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

- 10) Supplied as a design limit, but not guaranteed or tested.

# UT54ACS164245SEI

### AC Electrical Characteristics \*1 (Port B = 5 Volt, Port A = 3.3 Volt)

$(V_{DD1} = 5V \pm 10\%; V_{DD2} = 3.3V \pm 0.3V)$  (T<sub>c</sub> = -55°C to +125°C for "C" screening and -40°C to +125°C for "W" screening)

| Symbol                          | Parameter                                                  | MIN      | MAX       | Unit |

|---------------------------------|------------------------------------------------------------|----------|-----------|------|

|                                 |                                                            | UT54ACS: | L64245SEI |      |

| t <sub>PLH</sub>                | Propagation delay Data to Bus                              | 3.5      | 11        | ns   |

| t <sub>PHL</sub>                | Propagation delay Data to Bus                              | 3.5      | 11        | ns   |

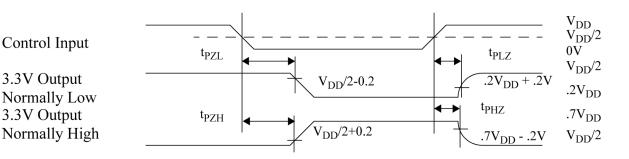

| t <sub>PZL</sub>                | Output enable time OEx to Bus                              | 2.5      | 16        | ns   |

| $t_{\text{PZH}}$                | Output enable time OEx to Bus                              | 2.5      | 16        | ns   |

| t <sub>PLZ</sub>                | Output disable time $\overline{OE}x$ to Bus high impedance | 2.5      | 16        | ns   |

| t <sub>PHZ</sub>                | Output disable time $\overline{OE}x$ to Bus high impedance | 2.5      | 16        | ns   |

| $t_{PZL}^2$                     | Output enable time DIRx to Bus                             | 1        | 18        | ns   |

| t <sub>PZH</sub> <sup>2</sup>   | Output enable time DIRx to Bus                             | 1        | 18        | ns   |

| t <sub>PLZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 20        | ns   |

| t <sub>PHZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 20        | ns   |

| t <sub>SKEW</sub> <sup>3</sup>  | Skew between outputs                                       | -        | 600       | ps   |

| t <sub>DSKEW</sub> <sup>4</sup> | Differential skew between outputs                          | -        | 1.5       | ns   |

- 1) All specifications valid for radiation dose  $\leq$  1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) DIRx to bus times are guaranteed by design, but not tested. OEx to bus times are tested

- 3) Output skew is defined as a comparison of any two output transitions of the same type at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus high-to-low and low-to-high versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

- 4) Differential output skew is defined as a comparison of any two output transitions of opposite types at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

# UT54ACS164245SEI

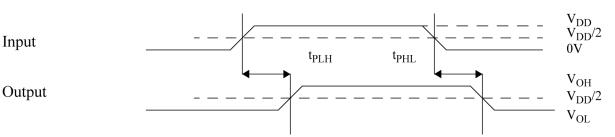

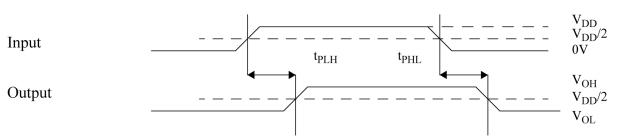

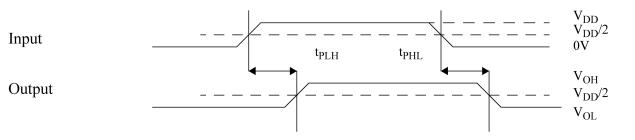

# **Propagation Delay**

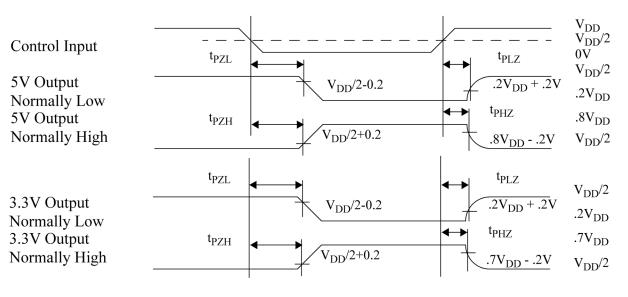

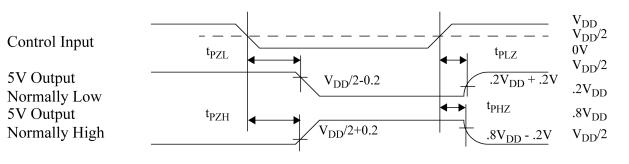

# **Enable Disable Times**

# UT54ACS164245SEI

## AC Electrical Characteristics \*1 (Port A = Port B, 5 Volt Operation)

$(V_{DD1} = 5V \pm 10\%; V_{DD2} = 5.0V \pm 10\%)$  (T<sub>c</sub> = -55°C to +125°C for "C" screening and -40°C to +125°C for "W" screening)

| Symbol                          | Parameter                                                  | MIN      | MAX       | Unit |

|---------------------------------|------------------------------------------------------------|----------|-----------|------|

|                                 |                                                            | UT54ACS: | L64245SEI |      |

| t <sub>PLH</sub>                | Propagation delay Data to Bus                              | 3.5      | 9         | ns   |

| t <sub>PHL</sub>                | Propagation delay Data to Bus                              | 3.5      | 9         | ns   |

| t <sub>PZL</sub>                | Output enable time OEx to Bus                              | 3        | 9         | ns   |

| t <sub>PZH</sub>                | Output enable time OEx to Bus                              | 3        | 9         | ns   |

| $t_{PLZ}$                       | Output disable time $\overline{OE}x$ to Bus high impedance | 3        | 9         | ns   |

| t <sub>PHZ</sub>                | Output disable time $\overline{OE}x$ to Bus high impedance | 3        | 9         | ns   |

| t <sub>PZL</sub> 2              | Output enable time DIRx to Bus                             | 1        | 12        | ns   |

| t <sub>PZH</sub> <sup>2</sup>   | Output enable time DIRx to Bus                             | 1        | 12        | ns   |

| t <sub>PLZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 15        | ns   |

| t <sub>PHZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 15        | ns   |

| t <sub>skew</sub> <sup>3</sup>  | Skew between outputs                                       | -        | 600       | ps   |

| t <sub>DSKEW</sub> <sup>4</sup> | Differential skew between outputs                          | -        | 1.5       | ns   |

- 1) All specifications valid for radiation dose  $\leq$  1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) DIRx to bus times are guaranteed by design, but not tested.  $\overline{\text{OE}}x$  to bus times are tested

- 3) Output skew is defined as a comparison of any two output transitions of the same type at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus high-to-low and low-to-high versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

- 4) Differential output skew is defined as a comparison of any two output transitions of opposite types at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

# UT54ACS164245SEI

# **Propagation Delay**

# **Enable Disable Times**

## **Propagation Delay**

## **Enable Disable Times**

# UT54ACS164245SEI

### AC Electrical Characteristics \*1 (Port A = Port B, 3.3 Volt Operation)

$(V_{DD1} = 3.3V \pm 0.3V; V_{DD2} = 3.3V \pm 0.3V)$  (Tc = -55°C to +125°C for "C" screening and -40°C to +125°C for "W" screening)

| Symbol                          | Parameter                                                  | MIN      | MAX       | Unit |

|---------------------------------|------------------------------------------------------------|----------|-----------|------|

|                                 |                                                            | UT54ACS1 | L64245SEI |      |

| t <sub>PLH</sub>                | Propagation delay Data to Bus                              | 3.5      | 11        | ns   |

| t <sub>PHL</sub>                | Propagation delay Data to Bus                              | 3.5      | 11        | ns   |

| t <sub>PZL</sub>                | Output enable time OEx to Bus                              | 2.5      | 16        | ns   |

| t <sub>PZH</sub>                | Output enable time OEx to Bus                              | 2.5      | 16        | ns   |

| t <sub>PLZ</sub>                | Output disable time $\overline{OEx}$ to Bus high impedance | 2.5      | 16        | ns   |

| t <sub>PHZ</sub>                | Output disable time $\overline{OEx}$ to Bus high impedance | 2.5      | 16        | ns   |

| t <sub>PZL</sub> <sup>2</sup>   | Output enable time DIRx to Bus                             | 1        | 18        | ns   |

| t <sub>PZH</sub> <sup>2</sup>   | Output enable time DIRx to Bus                             | 1        | 18        | ns   |

| t <sub>PLZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 20        | ns   |

| t <sub>PHZ</sub> <sup>2</sup>   | Output disable time DIRx to Bus high impedance             | 1        | 20        | ns   |

| t <sub>SKEW</sub> <sup>3</sup>  | Skew between outputs                                       | -        | 600       | ps   |

| t <sub>DSKEW</sub> <sup>4</sup> | Differential skew between outputs                          | -        | 1.5       | ns   |

#### Notes:

\*For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1) All specifications valid for radiation dose  $\leq$  1E5 rad(Si) per MIL-STD-883, Method 1019.

- 2) DIRx to bus times are guaranteed by design, but not tested. OEx to bus times are tested.

- 3) Output skew is defined as a comparison of any two output transitions of the same type at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus high-to-low and low-to-high versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

- 4) Differential output skew is defined as a comparison of any two output transitions of opposite types at the same temperature and voltage for the same port within the same byte: 1A1 through 1A8 are compared high-to-low versus low-to-high; similarly 1B1 through 1B8 are compared, 2A1 through 2A8 are compared, and 2B1 through 2B8 are compared.

# UT54ACS164245SEI

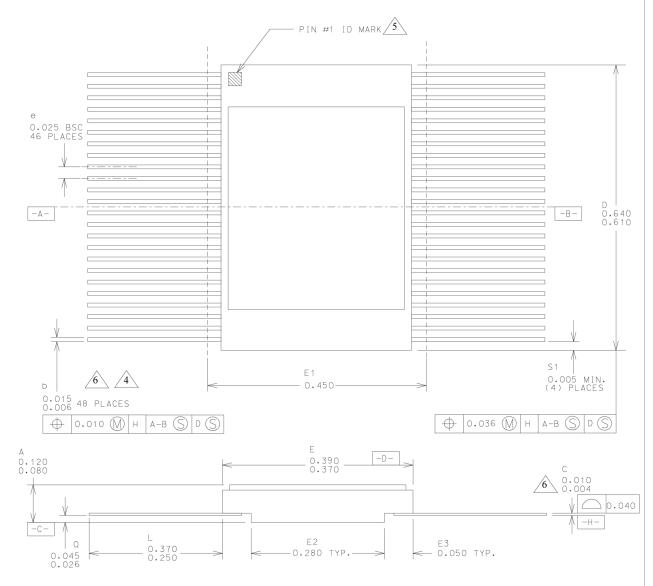

# Package

#### Figure 1. 48-Lead Flatpack

- 1) All exposed metalized areas are gold plated over electroplated nickel per MIL-PRF-38535.

- 2) The lid is electrically connected to VSS.

- 3) Lead finishes are in accordance with MIL-PRF-38535.

- 4) Lead position and colanarity are not measured.

- 5) ID mark symbol is vendor option.

- 6) With solder, increase maximum by 0.003.

DATASHEET

Schmitt CMOS 16-bit Bidirectional MultiPurpose Transceiver

# UT54ACS164245SEI

## **Ordering Information**

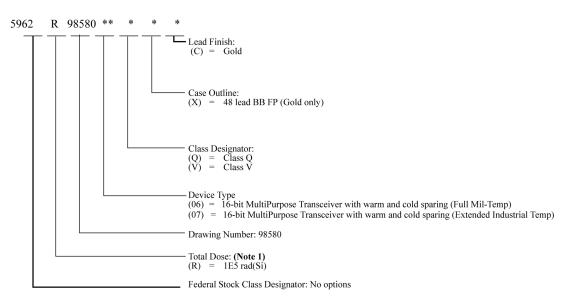

## UT54ACS164245SEI: SMD

#### Note:

1) Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening.

# UT54ACS164245SEI

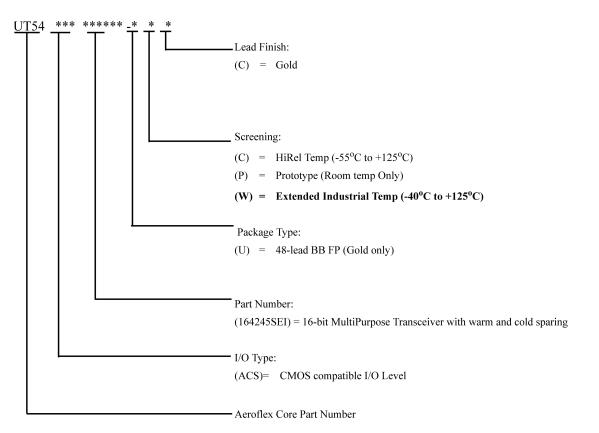

## UT54ACS164245SEI

- 1) HiRel Temperature Range flow per CAES Colorado Springs Manufacturing Flows Document. Devices are tested -55C, room temp, and 125C.Radiation neither tested nor guaranteed.

- 2) Extended Industrial Temperature Range Flow per CAES Manufacturing Flows Document. Devices are tested at -40°C, room temp, and +125°C. Radiation is neither tested nor guaranteed.

- 3) Extended Industrial Range flow per CAES Colorado Springs Manufacturing Flows Document. Devices are tested at -40°C, room temp, and 125°C.Radiation neither tested nor guaranteed.

**RELEASED 4/16**

Schmitt CMOS 16-bit Bidirectional MultiPurpose Transceiver

# UT54ACS164245SEI

## Datasheet Definitions

|                       | DEFINITION                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet <b>is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                             |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.