| PRODUCT NAME   | MANUFACTURER<br>PART NUMBER | SMD #      | DEVICE TYPE | INTERNAL PIC<br>NUMBER |

|----------------|-----------------------------|------------|-------------|------------------------|

| Arm Cortex M0+ | UT32M0R500                  | 5962-17212 | NFC Unit    | QS30                   |

**Table 1: Cross Reference of Applicable Products**

### 1.0 Overview

The NOR Flash Controller (NFC) interfaces to the external UT8QNF8M8 64 Mbit NOR Flash Memory (NFM). The NFC is a bridge between NFM and AHB bus and provides the functionality to control and access the Flash using the JEDEC 42.4 Flash command set standard. It supports read, nvmem reset, program and sector erase of the 11 Nor Flash Commands. The NFC provides the data interface and control protocols to operate the NOR Flash via the Nor Flash Memory I/O.

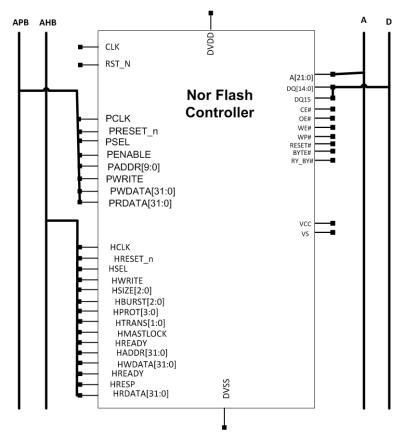

Figure 1 shows the basic diagram of the NOR FLASH MCTLR.

Figure 1: MTCLT

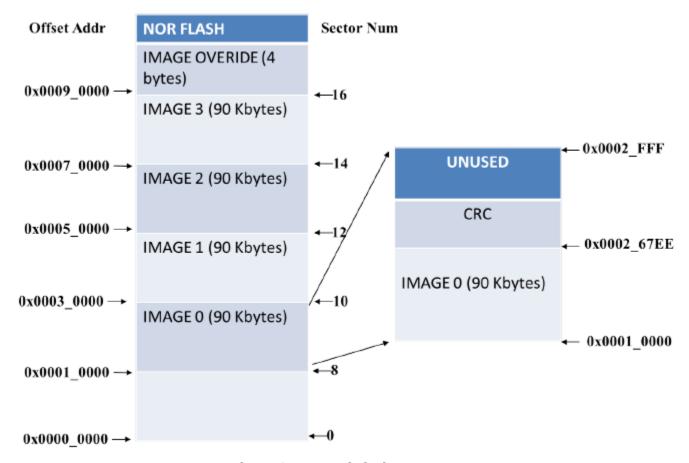

The NFM (UT8QNF8M8) is divided into four images, see figure 2. Each image is 90Kbytes and has a CRC checksums associated with it at 90K offset from the image start address, i.e., 0x0002\_67EE from 0x0001\_0000. Each image occupies 2 sectors of 64Kbytes each for a total of 128Kbytes. At the start of sector 16, address 0x0009\_0000, 4 bytes are reserved for image override. This gives the user flexibility for updating one or more of the images.

Figure 2: External Flash memory map

### 2.0 Application Note Layout

This application note (AN) provides a brief description of the NFC unit's memory map, configuration and programming.

#### 3.0 NFC Unit Hardware

The NFC Unit is mapped to the memory region from 0x4000\_C000 to 0x4000\_CFFF. It has 21 registers, see Table 2. For more information on each register, refer to **Chapter 14** of the UT32R500 Functional Manual.

| Offset  | Register        | Offset              | Register                                   |

|---------|-----------------|---------------------|--------------------------------------------|

| 0x00000 | NFC_CONTROL     | 0x00000             | NFC Control Register                       |

| 0x00004 | NFC_STATUS      | 0x00004             | NFC Status Register                        |

| 0x00008 | NFC_SECTOR_ADDR | 0x00008             | NFC Sector Address Register                |

| 0x00020 | NFC_TEST_ID     | 0x00020             | NFC Test ID Register                       |

| 0x00024 | NFC_TEST_ERR    | 0x00024             | NFC Test Error Register                    |

| 0x00FC0 | PERIPH ID0-ID15 | 0x00FC0-<br>0x00FFC | NOR Flash Peripheral ID0 to ID15 Registers |

Table 2: UT32M0R500 NFC Registers

### 3.1 NFC Unit Control Register

Enable Flash output drivers: OE#, WE# and CE by setting bit CONTROL[9] to 0; Reset NFC by toggling bit CONTROL[0] from 0 to 1; Power-up the NOR Flash by setting bit CONTROL[16] to 1, then delay to allow it finish powering up; Reset the NOR Flash by toggling bit CONTROL[1] to 1: the bit resets itself at the end of the operation.

### 3.2 NFC Unit Status Register

To wait for the last pending operation to complete, check bit STATUS[0]: 1 indicates NOR flash is idle; 0 indicates the NOR Flash is busy waiting.

### 3.3 NFC Unit Sector Register

Sector Address Register (SECTOR\_ADDR) in the core sets the corresponding sector address of the external NOR Flash to do an erase, read or write.

### 3.3.1 NFC Peripheral ID Registers

Each Peripheral ID Register (PERIPH ID0) is one of 16 registers (PERIPH ID0-15).

#### 4.0 NFC Unit Initialization

The NFC is initialized for image number, access size—8 or 16 bits, and if powered down, powering up the external NOR Flash.

Code 1 initializes the NFC to interface to the external NOR Flash (UT8QNF8M8).

```

NFC_StructInit (&NFC_InitStruct);

NFC_InitStruct.ImageNumber = CurrentImageNumber;

// init the NFC

NFC_Error = NFC_Init (NFC, &NFC_InitStruct);

```

#### Code 1: NFC Initialization

### 5.0 NFC Unit Programming

**Section 3.0** presented some of the basic configurations for the NFC core and each of the NFC registers. The following sections show programming examples by making use of Cobham API's for the UT32RM0R500 NFC Controller.

#### 5.1 NFC Write Word

The API provides a function for writing bytes or words to the external flash. The function in Code 2 references the NFC structure, sets the address to write to and copies the data, whether it is a byte or word to write to flash and the number of bytes to write.

```

// write the word

NFC_Error = NFC_WriteToFlash (NFC, Address, (void *) &Data,

sizeof (uint16_t));

```

#### Code 2: Write

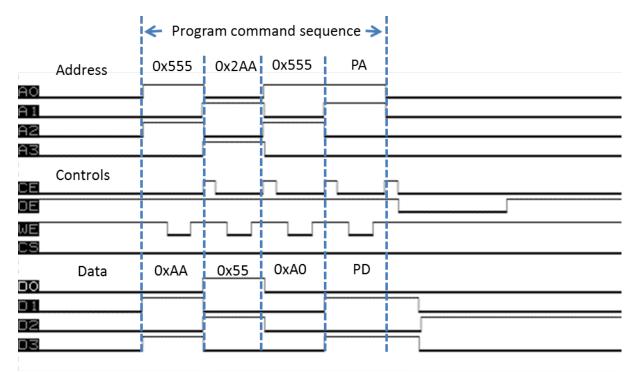

Internally, the API finds the sector address and 8 or 16 bit write; Then enables the flash for write, sends the byte(s) over the AHB bus to Flash and waits for the operation to complete; finally, disables flash writes. Figure 3 shows the Oscilloscope timing diagram for writing to External Flash. The diagram shows the 4 cycle program command sequence.

**Figure 3: Program Command Sequence Timing Diagram**

#### 5.2 NFC Read Word

The API provides a function for reading bytes or words to the external flash. The function in Code 3 references the NFC structure, sets the address to read to, references where to put data, whether it is a byte or word to read from flash and the number of bytes to read.

```

// read the word

NFC_Error = NFC_ReadFromFlash (NFC, (void *) &Data,

Address, sizeof (uint16_t));

```

Code 3: NFC Write

Internally, the API finds the sector address and 8 or 16 bit read; Then enables the flash for read, receives the byte(s) over the AHB bus from Flash. Figure 4 show an Oscilloscope diagram of writing to the External Flash. The diagram shows the 1 cycle program command sequence.

#### **Read Command Sequence**

**Figure 4: Read Command Sequence Timing Diagram**

### 5.3 NFC Write Read Verify

For Write, Read and Verify, the user calls the same functions from Code 2 and Code 3 and compares the data written and read from the external flash.

Code 4 shows the comparison.

```

// compare the buffers, reuse Address

Address = memcmp (LargeWriteBuffer, LargeReadBuffer, Count);

if (Address == 0)

printf ("Write / Read / Verify cycle successful!!\r\n\r\n");

else

printf ("ERROR: Write / Read / Verify cycle unsuccessful...\r\n\r\n");

```

Code 4: Write, Read and Verify

Internally, the API repeats the stated statements for read and write from sections **Section 5.1 and Section 5.2.**

#### 5.4 NFC Read Block

For read block, the user calls the same functions from Code 2 and Code 3 and passes a pointer to the block of data to be read from the external flash, see Code 5.

```

// read the block

NFC_Error = NFC_ReadFromFlash (NFC, (void *) LargeReadBuffer,

Address, Count);

if (NFC_Error == NFC_ERR_NONE)

printf (" Data read...\r\n");

Else

printf ("ERROR: data read error: %d\r\n", NFC_Error);

```

#### **Code 5: Read Block from Flash**

Internally, the API repeats the stated statements for read and write from sections **Section 5.1 and Section 5.2.**

### 5.5 NFC Erase Image

The API provides a function for erasing an image, specified by the init function, see **Section 5.2**. The function in Code 6 calls the API to erase the particular image.

```

// erase the image (two sectors)

NFC_Error = NFC_EraseFlashImage (NFC);

if (NFC_Error == NFC_ERR_NONE)

printf ( "Image erased\r\n\r\n" );

else

printf ( "ERROR: image erase error: %d\r\n\r\n", NFC_Error);

```

#### **Code 6: Erase Image**

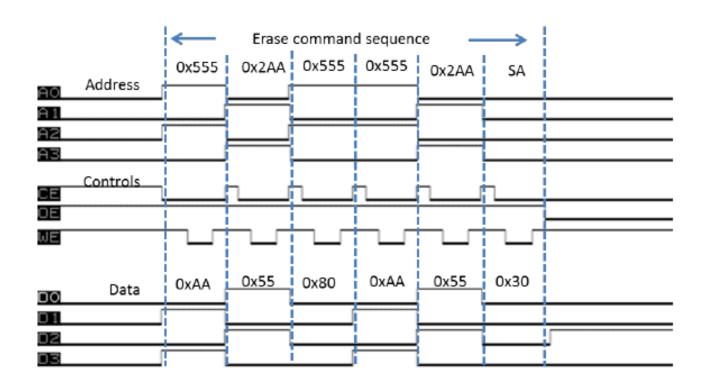

Internally, the API points to the base address of the beginning sector; disables write protect; enables erase for sector 1 and 2 of the particular image, then waits for the operation to complete; erases sector 1 followed by sector 2 of the particular image, then waits for the operation to complete; Finally, restores the image base sector address. Figure 5 show an Oscilloscope diagram of writing to the External Flash. The diagram shows the 6 cycle program command sequence.

**Figure 5: Erase Command Sequence Timing Diagram**

### 5.6 NFC Check Erase Image

All For Check Erase Image, the user calls the same functions from code 3, and reads every byte within the image space and compares it to 0xFF. Code 7 shows the comparison.

**Code 7: Image Compare**

Putting it all together: From a Terminal window, type ? and hit **Enter**. The terminal window displays all the commands for the functions stated in the previous sections, see Figure 6. Start with INIT –i# and test the rest of commands.

```

COM5:19200baud - Tera Term VT

Edit Setup Control Window

Valid commands (case sensitive):

Display Version:

Device to Process:

DEU -t#

specifies target device

for -t (type), # can

N: for NOR Flash

S: for SPI Flash

be:

Image to Process:

IMG -n#

specifies

for -n

ies image for next command series

-n (number), # is:

image number: 0..3

Erase Image:

erases image

Program Image:

to-be-uploaded image

- f (format), # can be:

H: for Intel Hex records

S: for Motorola S19 records

Compare Image:

compares image to a to-be-uploaded image

for -f (format), # can be:

H: for Intel Hex records

S: for Motorola $19 records

GRC -c####

embeds CRC into i

for -c (CRC),

four-digit

(A2C4,

CRC-Stamp Image:

image for verification

, #### MUST be:

t hexadecimal number, all CAPS

for example)

Verify Image:

use embedded CRC to verify image

Image Override:

OURD

specifies the override image number for -n (number), # is:

override image: 0..3

clear override: -1

if no argument, current override is displayed

FLD

forces loading of image specfifed in 'IMG' command

Force Load Image:

NFT -n# -a#

conducts NOR Flash reads or writes

for -n (number), # is:

image number: Ø..3

for -a (action), # can be:

NOR Flash Test:

Sector Addr Test:

conducts NOR Flash sector address test -- DESTRUCTIVE

SPI NURAM Test:

SNT -a#####

NURAM reads/writes -- DESTRUCTIU

ddress), ##### MUST be:

ligit hexadecimal number, all CAPS

PBA, for example)

conducts SPI

-- DESTRUCTIVE

Jump to SRAM Image: JMP

jumps to image loaded into SRAM at 0x20000000

```

Figure 6: NOR Flash Commands

Code 8 shows snippets of parsing the commands and calling the particular function.

```

uint8_t ProcessCommandLine (uint8_t ConsoleCommand) {

switch (ConsoleCommand)

case CCMD_DISPLAY_VERSION:

ConsoleDisplayVersionInfo ();

break:

case CCMD_INIT_NFC:

Ex_NFC_Init ();

break;

case CCMD_ERASE_IMAGE:

Ex_NFC_EraseImage ();

break;

case CCMD_CHECK_FOR_ERASED_IMAGE:

Ex_NFC_CheckForErasedImage ();

break;

case CCMD_WRITE_WORD:

Ex_NFC_WriteWord ();

break;

case CCMD READ WORD:

Ex_NFC_ReadWord ();

break;

case CCMD_READ_BLOCK:

Ex_NFC_ReadBlock ();

break;

case CCMD_WR_RD_VFY_BLOCK:

Ex_NFC_WriteReadVerify_Block ();

break;

default:

DisplayMenu ();

break;

if (! ConsoleQuietMode) sendstr ( "\r\n:>" );

return (ConsoleCommand);

```

**Code 8: Command Parsing**

### 6.0 Summary and Conclusion

The NFC provides the data interface and control protocols to operate the NOR Flash via the Nor Flash Memory I/O.

For more information about our UT32M0R500 microcontroller and other products, please visit our website: www.cobhamaes.com/HiRel.

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.